Estimating power after completing the fpga design – Altera PowerPlay Early Power Estimator User Manual

Page 15

Altera Corporation

2–7

October 2005

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

Setting Up PowerPlay Early Power Estimator for Stratix, Stratix GX & Cyclone FPGAs

Estimating Power After Completing the FPGA Design

When you complete your FPGA design, estimate the device power

consumption using the simulation-based power estimation feature in the

Quartus II software. The Quartus II Simulator supports simulation-based

power estimation for Stratix, Stratix GX, Cyclone, MAX

®

7000AE,

MAX 7000B, and MAX 3000A devices.

shows the advantages and disadvantages when using the

simulation-based power estimation feature in Quartus II software when

the FPGA design is complete.

f

For more information on the simulation-based power estimation feature

in Quartus II software, refer to the PowerPlay Early Power Estimator

chapter in the Quartus II Handbook.

1

Altera strongly recommends that you run the PowerPlay early

power estimator after your FPGA design is completed.

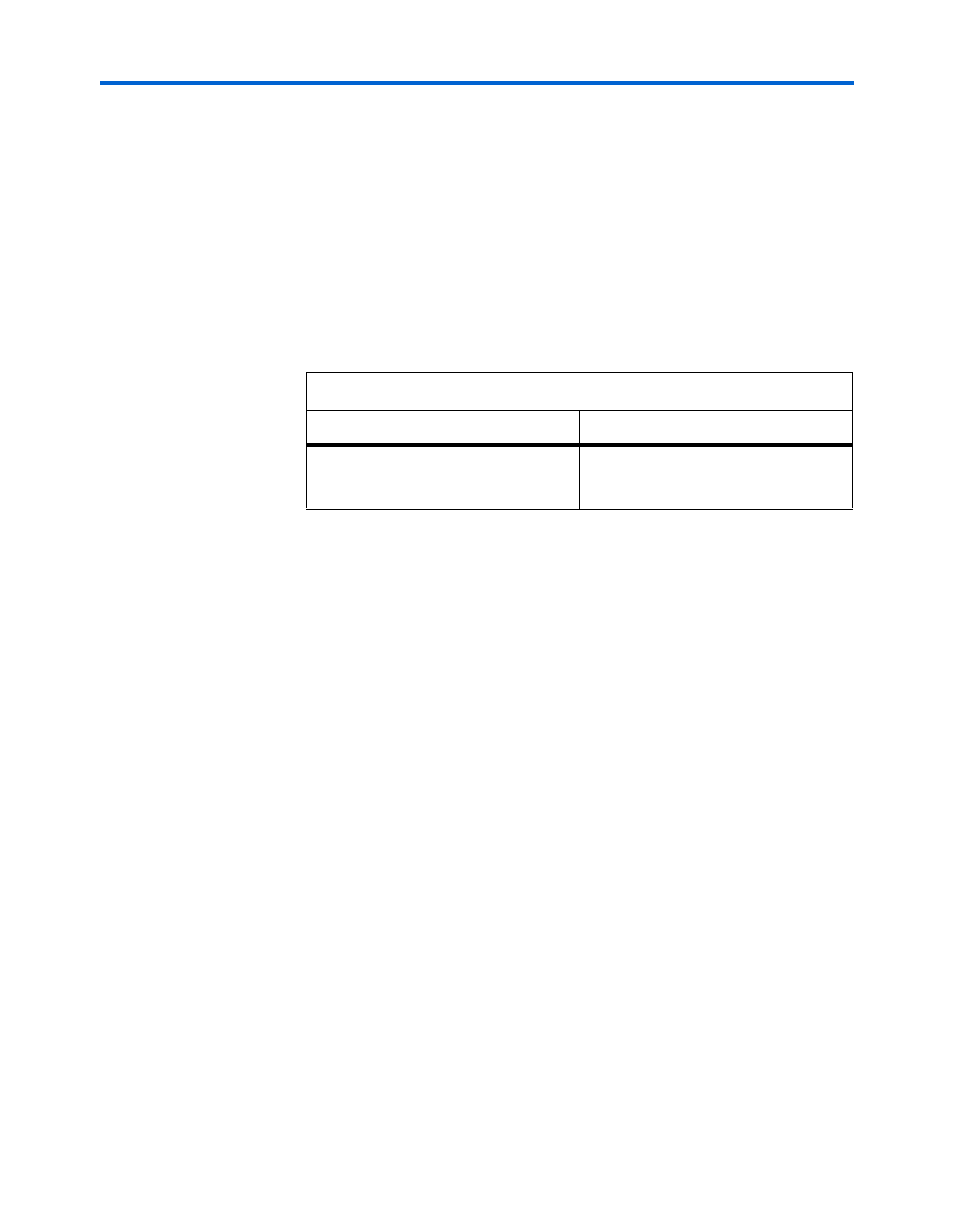

Table 2–3. Power Estimation When FPGA Design Is Complete

Advantages

Disadvantages

Provides the most accurate power

estimation since the simulation stimuli

reflects actual device behavior

Power estimation done later in the

FPGA design cycle