Sundance SMT370v2 User Manual

Page 31

Version 2.0

Page 31 of 46

SMT370v2/v3 User Manual

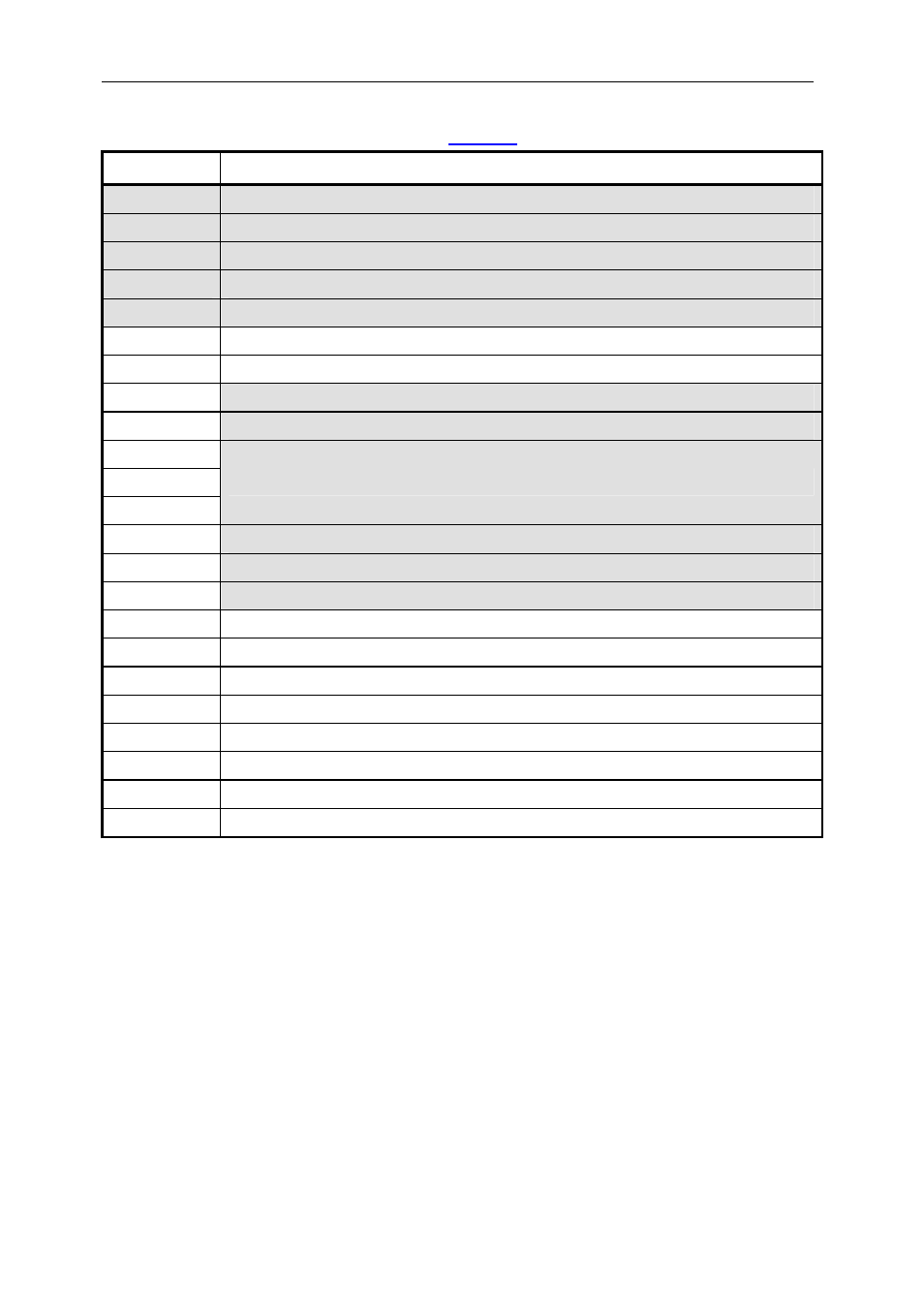

Register 0x1 – DAC register (report to

AD9777

datasheet for more details).

Note the Bit15 should be set to ‘0’ when there is no interpolation and to ‘1’ otherwise.

Bit number

Description

Bit 31

0

Bit 30

0

Bit 29

0

Bit 28

1

Bit 27-18

Not Used.

Bit 17

PLL Divide (Prescaler) Ratio.

Bit 16

PLL Divide (Prescaler) Ratio.

Bit 15

‘0’=PLL Off or ‘1’=PLL

Bit 14

‘0’=Automatic Charge Pump Control or ‘1’=Programmable.

Bit 13

Bit 12

Bit 11

Not Used.

Bit 10

PLL Charge Pump Control

Bit 9

PLL Charge Pump Control

Bit 8

PLL Charge Pump Control

Bit 7

IDAC Fine Gain. Adjustment

Bit 6

IDAC Fine Gain. Adjustment

Bit 5

IDAC Fine Gain. Adjustment

Bit 4

IDAC Fine Gain. Adjustment

Bit 3

IDAC Fine Gain. Adjustment

Bit 2

IDAC Fine Gain. Adjustment

Bit 1

IDAC Fine Gain. Adjustment

Bit 0

IDAC Fine Gain. Adjustment