Cpri v6.0 ip core reset requirements, Cpri v6.0 ip core reset requirements -5 – Altera CPRI v6.0 MegaCore Function User Manual

Page 35

CPRI v6.0 IP Core Reset Requirements

To reset the entire CPRI v6.0 IP core, you must assert the reset signals to the required external reset

controller logic. If you instantiate two Altera PHY Reset Controllers to implement this logic, one for the

TX data path and one for the RX data path, the user guide refers to the reset input signals to the two reset

controllers as

reset_tx

and

reset_rx

. Each of these two reset signals causes the reset logic to reset the

relevant data path of the IP core. However, the two signals are not direct input signals to the CPRI v6.0 IP

core.

In addition, some individual interfaces to the IP core have their own reset signals to reset only the

associated interface and logic.

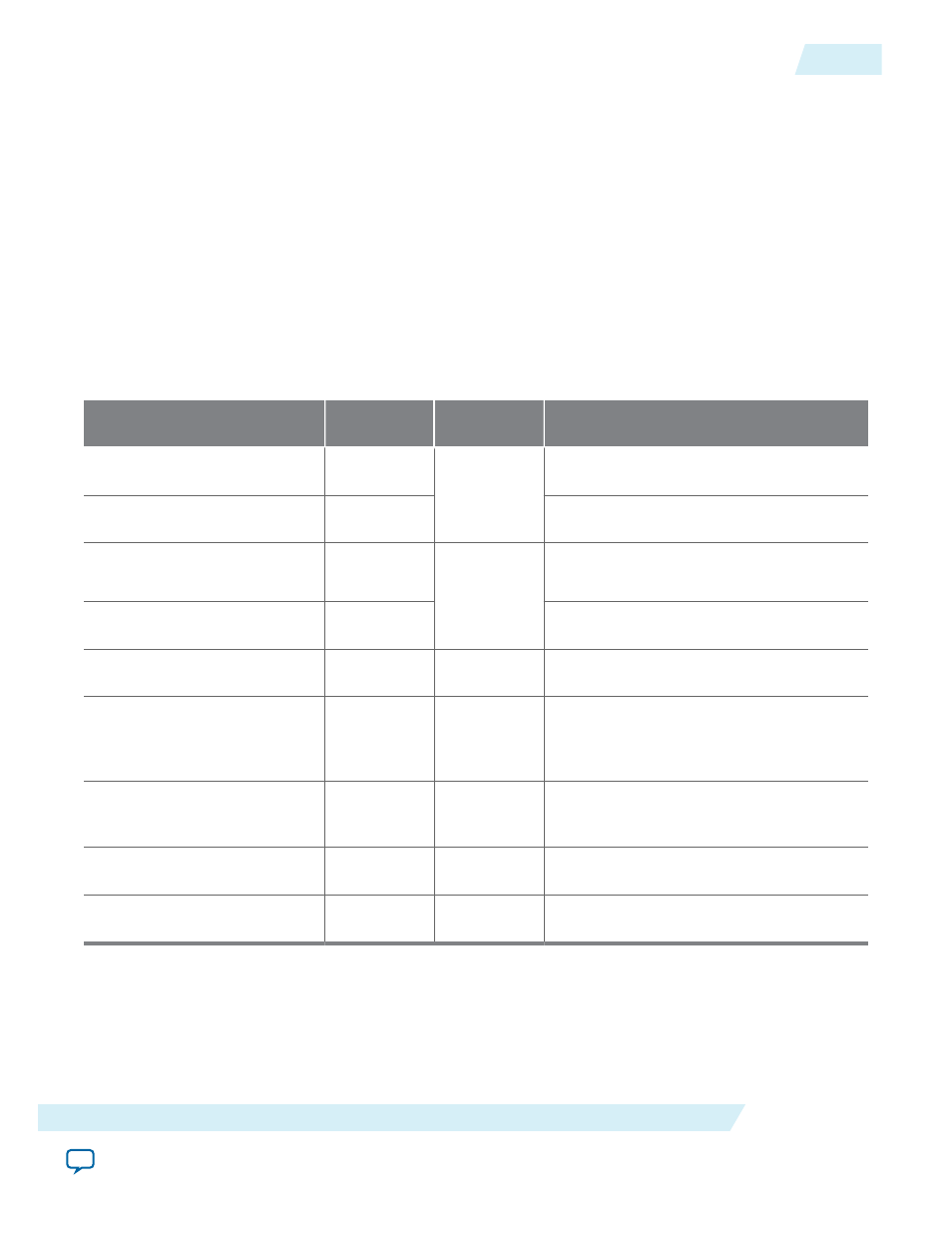

Table 3-3: CPRI v6.0 IP Core Reset Signals

You can assert all reset signals asynchronously to any clock. However, you must hold each reset signal asserted for

one full clock period of its associated clock, to ensure it is captured by the IP core.

CPRI v6.0 IP Core Reset Signal

Polarity

Associated

Clock

Information

xcvr_tx_analogreset

Active high

Analog reset to transmitter from external

reset controller.

xcvr_tx_digitalreset

Active high

Digital reset to transmitter from external

reset controller.

xcvr_rx_analogreset

Active high

Analog reset to receiver from external

reset controller.

xcvr_rx_digitalreset

Active high

Digital reset to receiver from external

reset controller.

ex_delay_reset

Active low

ex_delay_

clk

Resets the extended delay measurement

block.

reconfig_reset

Active high

reconfig_

clk

Asynchronous reset signal. Resets the

CPRI v6.0 Arria 10 transceiver reconfigu‐

ration interface and all of the registers to

which it provides access.

cpu_reset

Active low

cpu_clk

Resets the CPRI v6.0 CPU interface and

all of the registers to which it provides

access.

mii_txreset

Active low

mii_txclk

Resets the MII transmitter interface and

FIFO write logic.

mii_rxreset

Active low

mii_rxclk

Resets the MII receiver interface and

FIFO read logic.

UG-01156

2014.08.18

CPRI v6.0 IP Core Reset Requirements

3-5

Functional Description

Altera Corporation