Cm_status register, Start_up_seq register, Cm_status register -9 – Altera CPRI v6.0 MegaCore Function User Manual

Page 98: Start_up_seq register -9

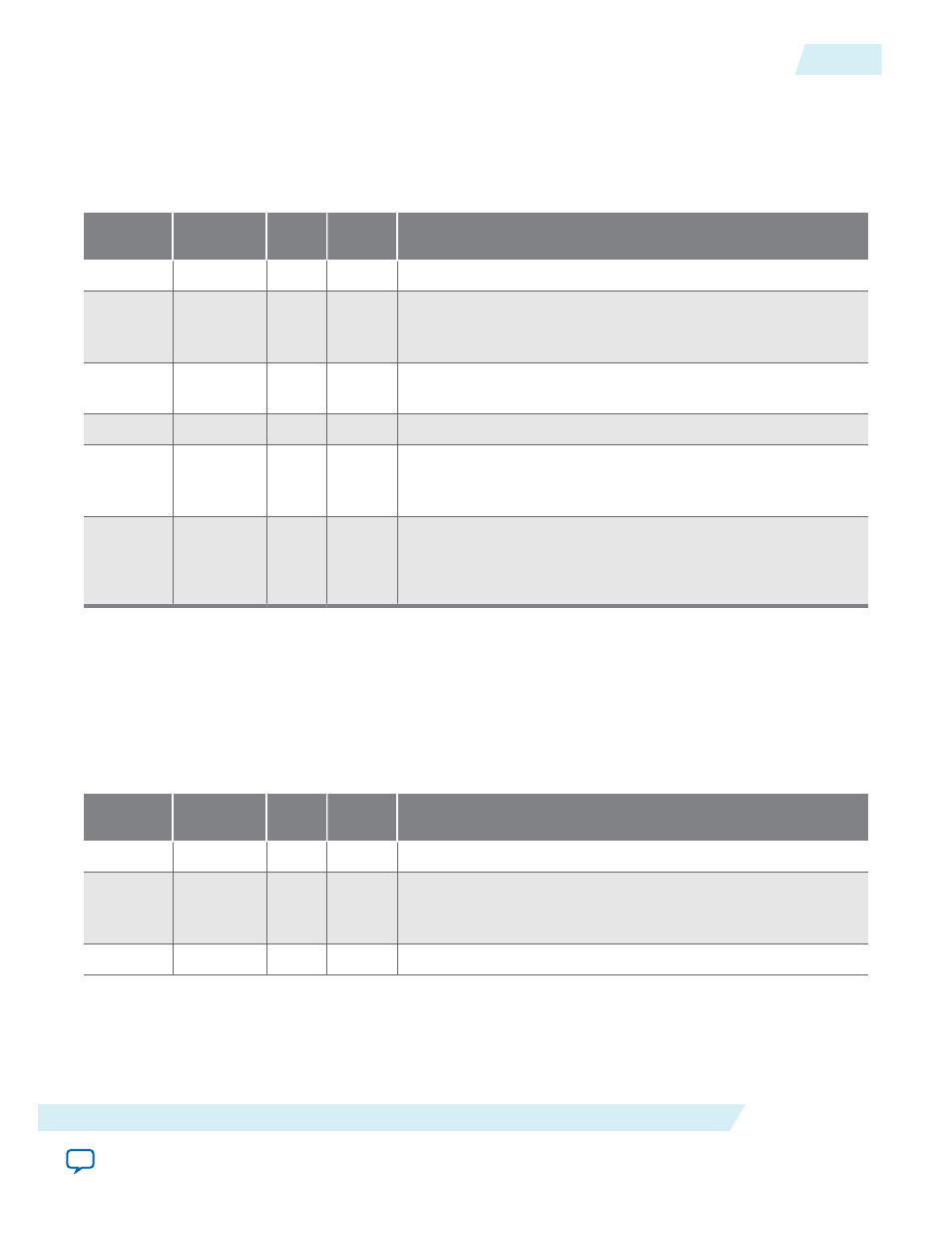

CM_STATUS Register

Table 5-11: CPRI v6.0 IP Core CM_STATUS Register at Offset 0x20

Bits

Field Name

Type

Value on

Reset

Description

31:12

Reserved

UR0

20'b0

11

rx_slow_

cm_rate_

valid

RO

1'b0

Indicates that a valid HDLC rate has been accepted.

10:8

rx_slow_

cm_rate

RO

3'b0

Accepted received HDLC rate.

7

Reserved

UR0

1'b0

6

rx_fast_

cm_ptr_

valid

RO

1'b0

Indicates that a valid Ethernet rate has been accepted.

5:0

rx_fast_

cm_ptr

RO

6'b0

Accepted received Ethernet rate.

Valid values are between 0x24 (decimal 20) and 0x3F (decimal

63), inclusive.

START_UP_SEQ Register

Table 5-12: CPRI v6.0 IP Core START_UP_SEQ Register at Offset 0x24

This register is available only if you turn on Enable start-up sequence state machine in the CPRI v6.0 parameter

editor.

Bits

Field Name

Type

Value on

Reset

Description

31:17

Reserved

UR0

15'b0

16

startup_

timer_

expired

RO

1'b0

Indicates that the itnernal L1 start-up timer is expired, based on

the value of the

startup_timer_period

field of the

START_UP_

TIMER

register.

15:11

Reserved

UR0

5'b0

UG-01156

2015.02.16

CM_STATUS Register

5-9

CPRI v6.0 IP Core Registers

Altera Corporation