Scsi chip id (scid), Scsi chip id, Scid) – Avago Technologies LSI8751D User Manual

Page 130

5-14

SCSI Operating Registers

If the SCSI clock doubler is enabled, use the desired

frequency after doubling to determine the conversion

factor.

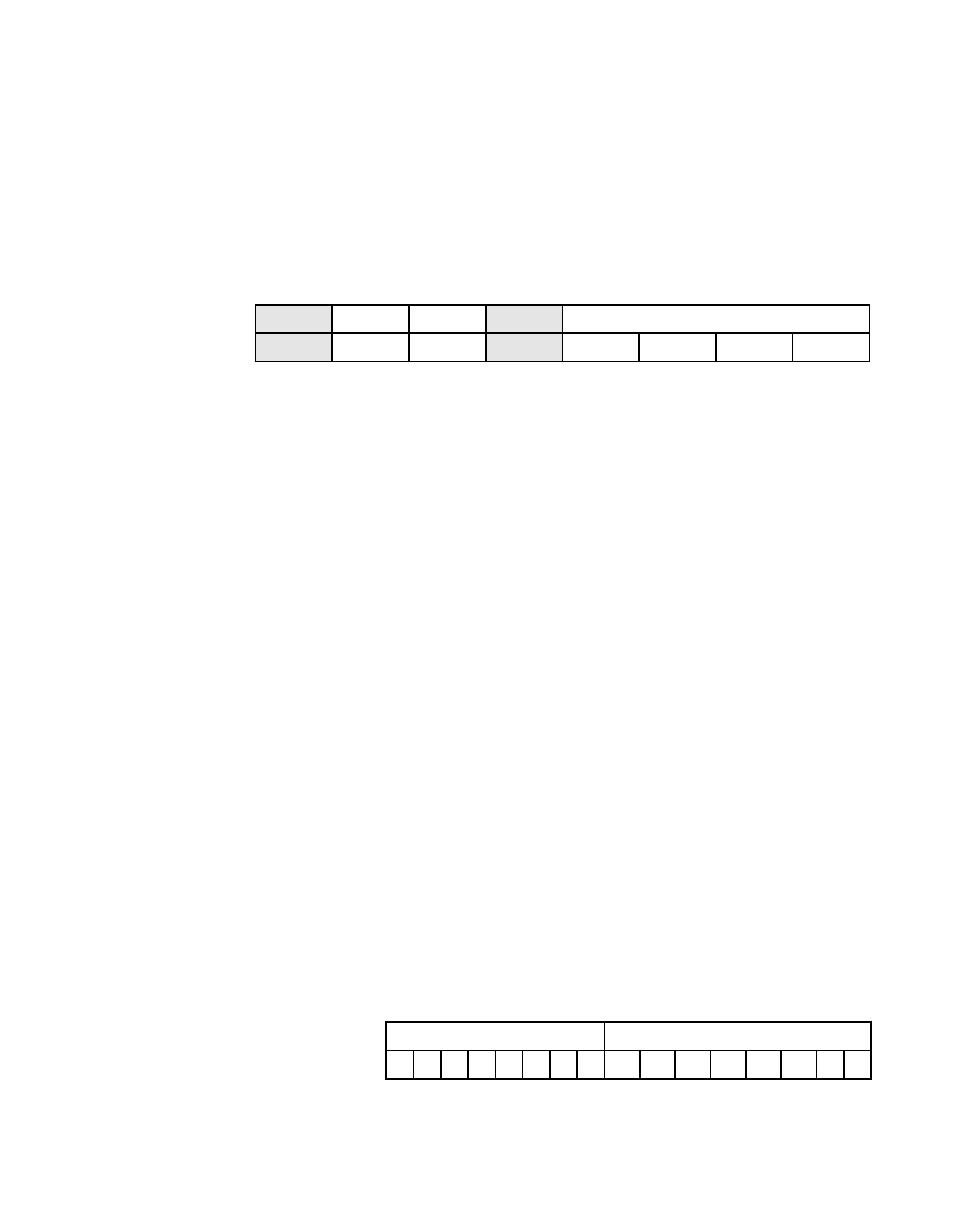

Register: 0x04 (0x84)

SCSI Chip ID (SCID)

Read/Write

R

Reserved

7

RRE

Enable Response to Reselection

6

When this bit is set, the LSI53C875 is enabled to respond

to bus-initiated reselection at the chip ID in the

and

registers. Note that the chip does not automatically

reconfigure itself to initiator mode as a result of being

reselected.

SRE

Enable Response to Selection

5

When this bit is set, the LSI53C875 is able to respond to

bus-initiated selection at the chip ID in the

and

registers. Note that the chip does not automatically

reconfigure itself to target mode as a result of being

selected.

R

Reserved

4

ENC[3:0]

Encoded Chip SCSI ID

[3:0]

These bits are used to store the LSI53C875 encoded

SCSI ID. This is the ID which the chip asserts when

arbitrating for the SCSI bus. The IDs that the LSI3C875

responds to when being selected or reselected are

configured in the

and

registers. The priority of

the 16 possible IDs, in descending order is:

7

6

5

4

3

0

R

RRE

SRE

R

ENC

x

0

0

x

0

0

0

0

Highest

Lowest

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8