Altera Transceiver PHY IP Core User Manual

Page 289

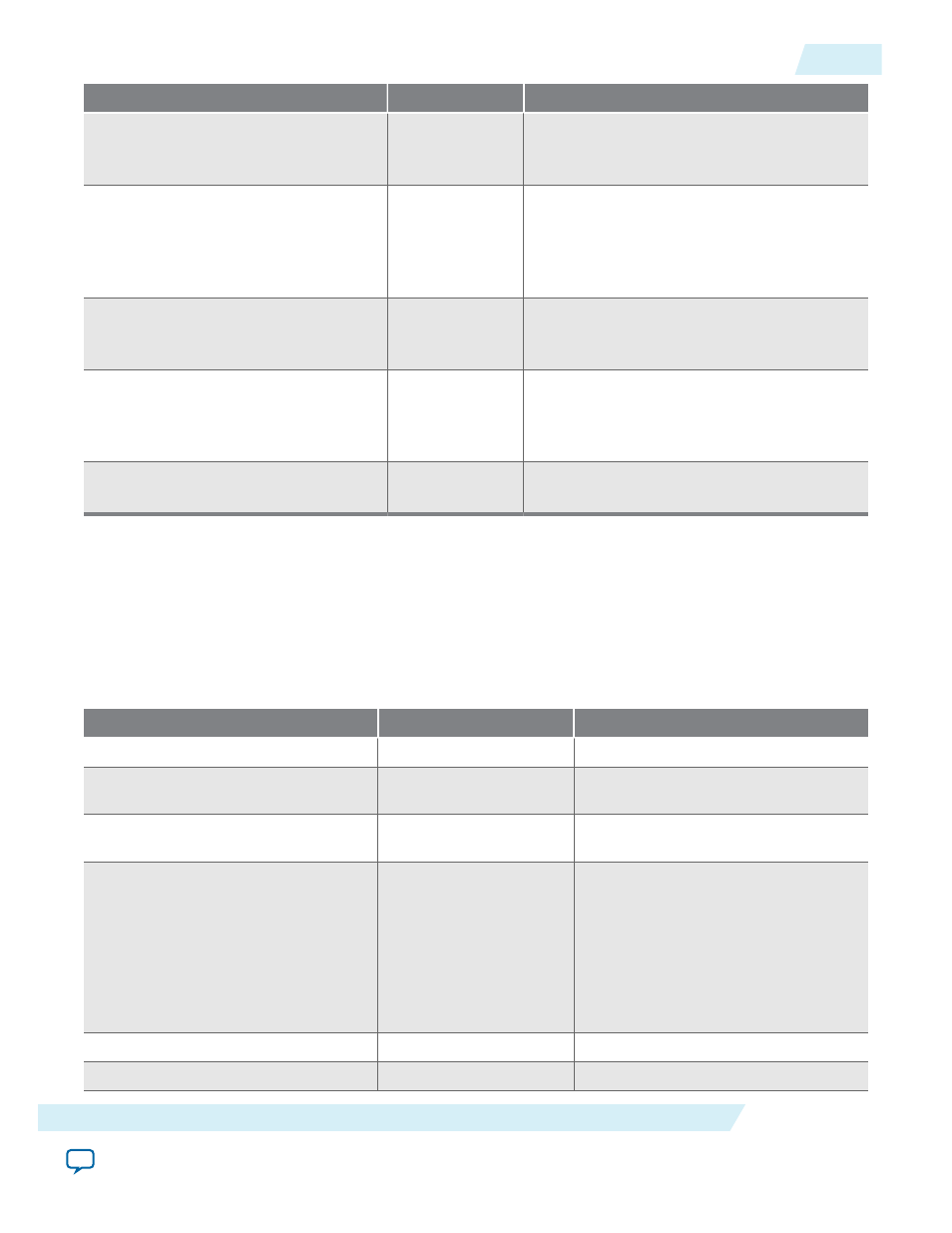

Signal Name

Direction

Signal Name

rx_is_lockedtoref [(<n>(<d>/<s>)

-1:0]

Output

Asserted when the receiver CDR is locked to

the input reference clock. This signal is

asynchronous. This signal is optional.

rx_is_lockedtodata [(<n><d>/<s>)

-1:0]

Output

When asserted, the receiver CDR is in to

lock-to-data mode. When deasserted, the

receiver CDR lock mode depends on the

rx_

locktorefclk

signal level. This signal is

optional.

rx_patterndetect [(<n>(<d>/<s>)-

1:0]

Output

When asserted, indicates that the

programmed word alignment pattern has

been detected in the current word boundary.

rx_rlv [<n> -1:0]

Output

When asserted, indicates a run length

violation. Asserted if the number of consecu‐

tive 1s or 0s exceeds the number specified

using the MegaWizard Plug-In Manager.

rx_runningdisp [(<n>(<d>/<s>)-

1:0]

Output

This status signal indicates the disparity of

the incoming data.

Optional Reset Control and Status Interfaces for Deterministic Latency

PHY

The following table describes the signals in the optional reset control and status interface. These signals

are available if you do not enable the embedded reset controller.

Table 11-16: Avalon-ST RX Interface

Signal Name

Direction

Description

pll_powerdown [<n>-1:0]

Input

When asserted, resets the TX PLL.

tx_digitalreset [<n>-1:0]

Input

When asserted, reset all blocks in the

TX PCS.

tx_analogreset [<n>-1:0]

Input

When asserted, resets all blocks in the

TX PMA.

tx_cal_busy [<n>-1:0]

Output

When asserted, indicates that the

initial TX calibration is in progress. It

is also asserted if reconfiguration

controller is reset. It will not be

asserted if you manually re-trigger

the calibration IP. You must hold the

channel in reset until calibration

completes.

rx_digitalreset [<n>-1:0]

Input

When asserted, resets the RX PCS.

rx_analogreset [<n>-1:0]

Input

When asserted, resets the RX CDR.

UG-01080

2015.01.19

Optional Reset Control and Status Interfaces for Deterministic Latency PHY

11-21

Deterministic Latency PHY IP Core

Altera Corporation